�S������O�伯�ɶȺ͔Uɢˮƽ����ߣ��OӋ�ˆT������������߉����ĉ����������Ч�ʣ�ͬ�r���ͳɱ����ߴ��늴Ÿɔ_��EMI�����M���Դ�Ĺ����ܶȺ�Ч��������ߣ����OӋ�ˆT�F(xi��n)��Ҳ���R���鮐��(g��u)̎���ܘ�(g��u)�_�l(f��)��܉�Դ��Q����������(zh��n)���@Щ�ܘ�(g��u)���ܰ���ASIC��DSP��F(xi��n)PGA���������Ļ�ϡ�

���y(t��ng)��ʹ�ý�����DC / DC�D(zhu��n)�Q�����ܘ�(g��u)��늣������S���Դ܉�Ĕ�(sh��)���������ӣ����y(t��ng)�ķ���ʽ������DC / DC�D(zhu��n)�Q���c����IC�̓�(n��i)�����ⲿ����MOSFET�Լ��ⲿ늸���һ��ʹ�ú������-���ܺ��s�Һĕr��ȡ����֮���ǣ��OӋ�ˆT����ʹ�þ��ж����Դ܉�Ϳɾ�����������������DC / DC�D(zhu��n)�Q��ģ�K���Ը��õؿ���EMI���a(ch��n)���ğ������٣�ռ�ÿ��g��С��

���Č���BǶ��ʽ�OӋ���Դϵ�y(t��ng)����ӑՓ���N�����Լ��OӋ�ˆT��Ҫ���]�����أ�Ȼ���ٽ�B�����Ľ�����DC / DCģ�K��Ȼ������ʹ��Monolithic Power Systems��ʾ���O�����Ҫ����OӋ�ˆT��Ҫӛס���OӋ�Ͳ���ע����헣��Էdz���̶ȵذl(f��)�]�@Щģ�K�����܃�(y��u)�ݡ�

��ʲôǶ��ʽϵ�y(t��ng)��Ҫ�S���Դ܉

�T��5G��վ֮�Ƕ��ʽ�OӋּ��֧�������֙C�������B���O���ڼ�ͥ���I(y��)�Ԅӻ����Ԅ��{���܇���t(y��)�����������ܿɴ����O��ȑ����в������L�Ĕ�(sh��)��(j��)��Ҫ���վͨ��ʹ��48��ݔ���Դ��ԓݔ���Դ��DC / DC�D(zhu��n)�Q��������24����12����Ȼ���Mһ��������������3.3��������1�����S����܉���Ԟ�ASIC��F(xi��n)PGA��늣�DSP�������O��̎�ڻ���̎���A�Ρ�ͨ�����Դ܉��Ҫ������M�І��Ӻ��P�]���@�Mһ���������OӋ�ˆT���Դϵ�y(t��ng)���s�ԡ�

��5G��վ���������y(t��ng)��CPU�����џo���M��̎��Ҫ���ǣ������ٿ��cFPGAһ��ʹ�þ���ϵ�y(t��ng)�����������ԣ��`���ԣ��_�l(f��)���ڶ̣��߶Ȳ���Ӌ��͵����t�ă�(y��u)�c�����ǣ�F(xi��n)PGA�Դ�Ŀ��ÿ��g���ڿsС�������Դ܉����Ҫ��Ҳ���s���D1����

ݔ��늉�ƫ�ƣ�늉�܉��ݔ��늉�ƫ�Ʊ��С��±3�����OӋ�Б���������������ͨ�^��(y��u)�����ƭh(hu��n)·�����ӎ������_���䷀(w��n)���ԣ�ȥ���������֔��ʹ�ú��OӋ��

���{(di��o)���ӣ�����늉�܉�Ć��ӱ�횆��{(di��o)�����������OӋ����ֹݔ��늉��������ʼֵ��

ݔ��늉��y�����ڷ�(w��n)�B(t��i)�����У�����늉�܉��ģ�M늉�܉���⣩��ݔ��늉��y����횷dz����10������mV����

�r���چ��Ӻ��P�]���g��F(xi��n)PGA��횝M���ض��ĕr��Ҫ��

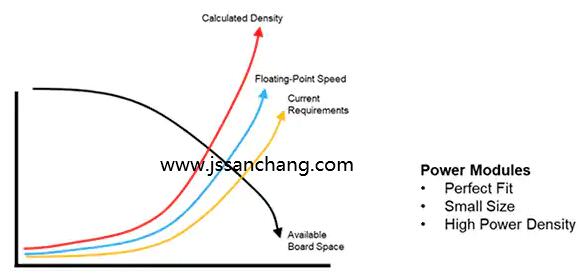

�D1�����ڲ������L��Ӌ�������ٿ��ϵ�̎�����ߴ������ˣ����]���Դ�������g��

�S����(sh��)��(j��)̎�펧������׃��Խ��Խ���̣�̎������Ҫ�����������ʡ����ٿ���Ӌ���ܶȺ��c�ٶ�Ҫ��Ҳ׃��Խ��Խ�y�Ԟ鹤�I(y��)���M�㡣���ٿ����ͨ����PCIe�˜ʻ��ģ���˰�ijߴ��ǹ̶��ġ����ڲ������L��Ӌ������̎�����ijߴ��ѽ�(j��ng)���ӣ����Դ�����Ŀ��g��С��

���ϵ�y(t��ng)�OӋ�������

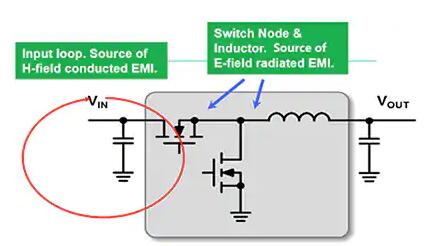

�����y(t��ng)���xɢ������DC / DC�D(zhu��n)�Q���c����IC�̓�(n��i)�����ⲿ����MOSFET�Լ��ⲿ늸����������һ��ʹ����Ƕ��ʽϵ�y(t��ng)��늵�һ�N����������������������Ҫ��܉�Դ��Q�������OӋ�ˆT���f���@��һ�����s�Һĕr���^�̡����˿��]Ч�ʷdz��ͽ�Q�����ߴ�dz�С��֮�⣬�OӋ�ˆT߀���ע��V�����M���IJ��ֺͲ��ã��Էdz�С���D(zhu��n)�Q����늸����·�е��_�P���������Ă�����ݗ��EMI���D2����

�D2�������Ľ�����DC / DC�D(zhu��n)�Q�������OӋ�ˆT��횹����Ķ���EMIԴ��

DC / DC�D(zhu��n)�Q��ͨ����ͨ�^�ň��a(ch��n)��������EMI��ԓ�ň������γ���ݔ������MOSFET�_�P��(ji��)�c�c��֮�g�Լ�ݔ��������c��֮�g������h(hu��n)·������߀��MOSFET�_�P��(ji��)�c��늸����B��֮�g�a(ch��n)��ݗ��늈�EMI��ԓݗ��늈�dV / dt�ߣ�����������ĸ�ݔ��늉��ƽ�ГQ���أ�����늸�����(n��i)���a(ch��n)����늴ň��Юa(ch��n)�����o�����_�OӋ���������ºĕr��EMI��������yԇ�Ͷ���OӋ������

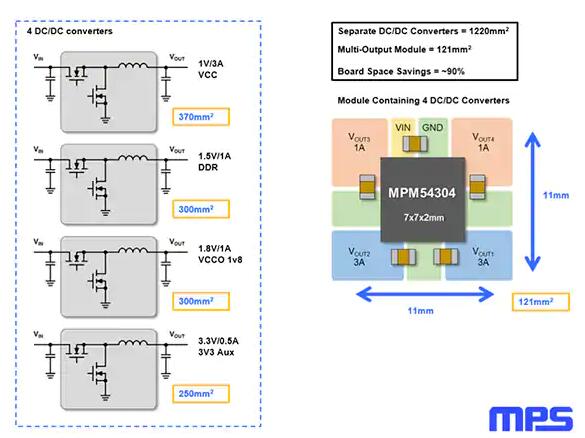

ʹ�÷����Ľ���DC / DC�D(zhu��n)�Q����ASIC��FPGA��늵���܉��Q������ռ��1220ƽ�����ף�mm 2�����D3����ʹ�û����Դ����IC��PMIC���Ľ�Q������ԓ�ߴ���ԜpС���s350 mm 2����������������OӋ�ˆT����ʹ�ê�������·ݔ��DC / DC�D(zhu��n)�Q��ģ�K����Q�����ߴ�pС���H121 mm 2��ͬ�r߀���Ժ����OӋ�^�̲��ӿ�a(ch��n)Ʒ���Еr�g���댧�w��ˇ���g�ͷ��b�Y(ji��)��(g��u)���M����ζ���dz���һ����DC / DCģ�K�Ժ�С�ijߴ猍�F(xi��n)�˷dz��ߵĹ����ܶȣ���Ч�ʺ����õ�EMI���ܡ�

�D3���c������Q������ȣ�ʹ�ü��ɵ�DC / DCģ�K��Q�������Թ�(ji��)ʡ���_90�����·����g��

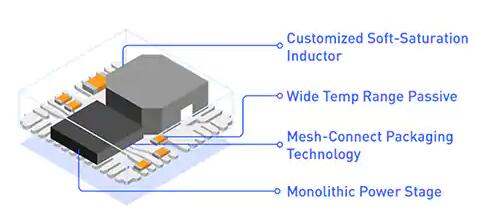

�µĘ�(g��u)�켼�g��������b��(n��i)���bоƬ��“�W(w��ng)���B��”������ܼ��g����ζ�����Ԍ�IC��늸����͟oԴ����ֱ�Ӱ��b����������ϣ����o�������I�ϻ��~��ă�(n��i)��pc�壨�D4���� �����cʹ�Ã�(n��i)��ӡˢ�·�����������I�ϵ��fʽ�Y(ji��)��(g��u)��ȣ��Ɍ��B���߾����L�Ȝp���dz��٣�����ֱ���B�����oԴԪ����ʹ늸б����^�ͣ��Ķ���EMI�����dz��͡�

�D4��������������M�л��B�����ͽY(ji��)��(g��u)�����S����(y��u)�c�����Ը��õؿ���EMI������ɢ�ᣬ���pСռλ��e��

�c��ֱ��ݗ����EMI���������������ֱ��ʽ��SIL����SIL���b��SIP����ʽ���D(zhu��n)�Q����ȣ�ʹ��ֱ�ӱ��氲�b��Ŀ��PCB�ĺ��P�Ÿ���У�LGA�����b��ʽ�ɽ���EMI�ֲ���

��·ݔ���ɾ��̼���DC / DCģ�K

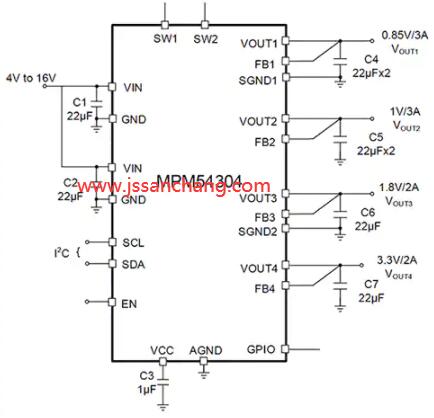

���˝M��Ƕ��ʽϵ�y(t��ng)�Ķ�܉���߹����ܶ������OӋ�ˆT����������MPM54304����Monolithic Power Systems���D5����MPM54304��һ���������Դ����ģ�K���������Ă���Ч��������DC / DC�D(zhu��n)�Q����늸������`���߉�ӿڡ�MPM54304����4����16����ݔ��늉�������(n��i)��������֧��0.55����7����ݔ��늉��������Ă�ݔ��܉��֧�ָ��_3���ࣨA����3 A��2 A��2 A��������ɂ�3 A܉�̓ɂ�2 A܉�ɲ�(li��n)�Էքe�ṩ6 A��4A���OӋ�ˆT��ע�⣬��(li��n)ģʽ�µķdz���ݔ�����Ҳ�ܵ������ĵ����ơ��@�ṩ�����ɎNݔ�����õ��`���ԣ��ܿ��������ƣ���

3 A��3 A��2 A��2 A

3 a��3 A��4 A

6 A��2 A��2 A

6 A��4 A

�D5��MPM54304��������4V��16Vݔ����·ݔ���������Դ����ģ�K��

MPM54304߀�醢�Ӻ��P�]�ṩ��(n��i)������܉�����ú��������ͨ�^��οɾ��̣�MTP����ӱ��U�z��ͨ�^I 2 C�����M���A���̡�

ԓ�̶��l�ʺ㶨��ͨ�r�g��COT������DC / DC�D(zhu��n)�Q�����ṩ���ٵ�˲�B(t��i)푑�����Ĭ�J��1.5��Ɲ��MHz���_�P�l�ʴ��pС���ⲿ������ijߴ硣���B�m(x��)���ģʽ��CCM���������g���_�P�r犱��i��������buck 1����buck 4��ݔ��늉���ͨ�^I 2 C�����{(di��o)��(ji��)����ͨ�^MTP��ӱ��U�z�A�á�

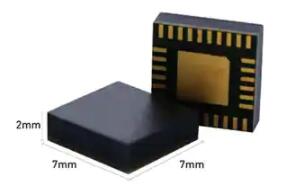

ȫ��ı��o���ܰ���Ƿ���i����UVLO�����^�����o��OCP���͟��P�C��MPM54304������ⲿ�M����(sh��)���dz��٣������ù�(ji��)ʡ���g��LGA��7 mm x 7 mm x 2 mm�����b�ṩ���D6����LGA�ĵͰ�����ʹ���m���ڰ����û�ɢ�����·���

�D6��MPM54304��LGA���b�ṩ��һ�N�o����С�ɵĽ�Q���������е�EMI

�OӋ�Ͳ���ע�����

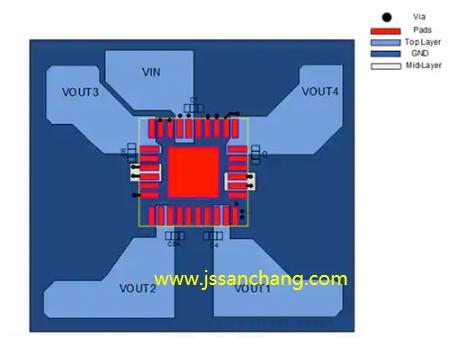

MPM54304��߅�����к��ε����_���У�ʹ���ֺ�PCB�OӋ�������ס�ֻ���傀�ⲿ�M����������Q������С���o����LGA���b���S�Թ̵Ľӵ،Ӹ��wģ�K�·��Ĵօ^(q��)���@�������]�Ϝu���h(hu��n)·���Mһ������EMI��

ԓ�����D(zhu��n)�Q�����в��B�m(x��)��ݔ�������������Ҫһ������������D(zhu��n)�Q���ṩ���������ͬ�r����ֱ��ݔ��늉����OӋ�ˆT��ʹ�õ͵�Ч��(li��n)��裨ESR����������@�÷dz������ܡ����]ʹ�þ���X5R��X7R늽��|(zh��)���մ�����������������ESR���Ҝض�ϵ��(sh��)С�����ڴ����(sh��)���ã�ʹ��22������µF�������������ˡ�

��Ч��ӡˢ�·�岼����MPM54304�ķ�(w��n)���\�����P��Ҫ�����hʹ���Č�ӡˢ�·���ԫ@�ø��õ�ɢ�����ܣ��D7�������˫@�÷dz��ѽY(ji��)�����OӋ�ˆT����ѭ���ʄt��

�����Դ�h(hu��n)·�M����С

Ոʹ���^��Ľӵ،�ֱ���B����PGND��������ǽӵ،ӣ��t��PGND���������^�ס�

�_��GND��VIN̎�Ĵ����·���߾��̣�ֱ�Ҍ�

�մ�ݔ����������M���ܿ�����������

ݔ����ݺ�IN���M���̶ܶ���

��VCC����������ڱM���ܿ���VCC��GND���_��λ��

��VIN��VOUT��GND�B�ӵ�����e���~���Ը��Ɵ����ܺ��L�ڿɿ���

��ݔ��GND�^(q��)���c플��ϵ�����GND�^(q��)����_����ͨ�^�����^�������ڃ�(n��i)���Ӻ͵����B����һ��

�_����(n��i)���ӻ�����м��ɵ�GND�^(q��)��

ʹ�ö����^���Դ���B�ӵ���(n��i)����

�D7��ʹ��MPM54304��·ݔ���Դģ�K�r�����hʹ���Č�ӡˢ�·�岼�֡�

�Y(ji��)Փ

�S��̎���wϵ�Y(ji��)��(g��u)�İl(f��)չ�Խ�Q���̵Ĕ�(sh��)��(j��)���������OӋ�ˆT���R���_�l(f��)��܉�Դ��Q����������(zh��n)��ԓ��Q��������֧���o�B(t��i)���տs��ʽ�����ӵ�̎������������O�䡣����DC / DC�D(zhu��n)�Q���Ǟ��@Щϵ�y(t��ng)�OӋ�Դ��Q�������P�I�M���������F(xi��n)�������ܺ��s��

��D��ʾ���OӋ�ˆT����ʹ�þ��ж����Դ܉�Ϳɾ������е�����������DC / DC�D(zhu��n)�Q��ģ�K���Ķ��������OӋ�^�̲��ӿ������Еr�g��ͬ�ӣ�ʹ�@Щ����ģ�K�ɞ���ܵ���(g��u)�켼�g�����S�����܃�(y��u)�ݣ����õؿ�����EMI��������ɢ�ᣬ���pС��ռ����e��